Gerbang logika atau gerbang logik adalah suatu entitas dalam elektronika dan matematika Boolean

yang mengubah satu atau beberapa masukan logik menjadi sebuah sinyal

keluaran logik. Gerbang logika terutama diimplementasikan secara

elektronis menggunakan diode atau transistor, akan tetapi dapat pula dibangun menggunakan susunan komponen-komponen yang memanfaatkan sifat-sifat elektromagnetik (relay), cairan, optik dan bahkan mekanik.

Gerbang elektronika

Untuk membangun sistem logika yang berfungsi secara penuh, relay, tabung hampa, atau transistor dapat digunakan. Contoh gerbang logika yaitu logika resistor-transistor (resistor-transistor logic / RTL), logika diode–transistor (diode-transistor logic / DTL), logika transistor-transistor (transistor-transistor logic / TTL), dan logika complementary metal–oxide–semiconductor (CMOS).Jenis-jenis gerbang logika

| Nama | Fungsi | Lambang dalam rangkaian | Tabel kebenaran | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| IEC 60617-12 | US-Norm | DIN 40700 (sebelum 1976) | ||||||||||||||||||

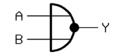

| Gerbang-AND (AND) |

|

|

|

|

||||||||||||||||

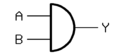

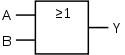

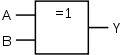

| Gerbang-OR (OR) |

|

|

|

|

|

|||||||||||||||

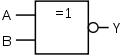

| Gerbang-NOT (NOT, Gerbang-komplemen, Pembalik(Inverter)) |

|

|

|

|

\

|

|||||||||||||||

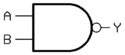

| Gerbang-NAND (Not-AND) |

|

|

|

|

|

|||||||||||||||

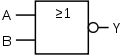

| Gerbang-NOR (Not-OR) |

|

|

|

|

|

|||||||||||||||

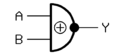

| Gerbang-XOR (Antivalen, Exclusive-OR) |

|

|

|

atau  |

|

|||||||||||||||

| Gerbang-XNOR (Ekuivalen, Not-Exclusive-OR) |

|

|

|

atau  |

|

|||||||||||||||

Tidak ada komentar:

Posting Komentar